Laporan Akhir 1 Percobaan 1 Kondisi 14

Laporan Akhir Percobaan 1 Kondisi 14

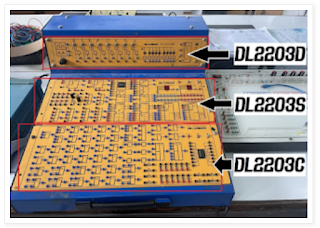

- Panel DL 2203D

- Panel DL 2203S

- Panel DL 2203C

- Jumper

3. Rangkaian Simulasi [Kembali]

Gambar rangkaian di atas merupakan gambar rangkaian J-K Flip Flop dan D Flip Flop dengan ketentuan input B0=1, B1=1, B2=0, B3=clock, B4=1, B5=1, B6=0. Flip Flop adalah rangkaian elektronika yang memiliki 2 kondisi stabil.

Rangkaian J-K Flip Flop pada kaki input R (Reset) itu terhubung dengan B0 yang bernilai 1, kaki input S (Set) terhubung dengan B1 yang bernilai 1, kaki input J terhubung dengan B2 yang bernilai 0, kaki input clock terhubung dengan B3 yang dimana clock tersebut aktif low dan syarat dari aktif low tersebut harus bernilai 0, kaki input K terhubung dengan B4 yang bernilai 1. Pada rangkaian J-K Flip Flop hal yang pertama kali diliat itu adalah clocknya apakah clocknya aktif low atau aktif high apabila aktif low maka syarat untuk aktifnya rangkaian tersebut harusnya bernilai 0, bahwa disini kaki input R maupun S itu bernilai 1 maka rangkaian tidak aktif dan output Q bernilai 0 sedangkan untuk output Q' bernilai 1 karena kebalikan dari output Q. Untuk kaki input J dan K tidak aktif dikarenakan inputnya tersebut bernilai 1 karena syarat aktif inputnya harus bernilai 0.

Rangkaian D Flip Flop pada kaki input D terhubung dengan B5 yang bernilai 1, kaki input clock terhubung dengan B6 yang bernilai 1. Pada D Flip Flop ini clocknya aktif high yang dimana syarat dari aktif high ini tersendiri inputnya harus bernilai 1 baru lah rangkaiannya dapat aktif, disini kaki input D bernilai 1 maka rangkaiannya aktif dan output Q bernilai 1 sedangkan untuk Q' bernilai 0 karena kebalikan dari output Q.

5. Video Rangkaian[Kembali]

1. Analisa apa yang terjadi saat input B3 dan B2 dihubungkan ke Clock dan K berlogika 1 gambarkan timing diagramnya.

Jawab:

Pada saat input B3 (CLK) dan B2 (J) dihubungkan ke Clock dan K bernilai 1, output dari rangkaian percobaan 1 Q bernilai 0 dan Q' bernilai 1. Karena output dari J-K Flip Flop terjadi pada saat fall time yang dimana fall time itu sendiri adalah kondisi dari high ke low, sehingga input J dan K akan selalu bernilai 0 dan 1, outputnya akan selalu bernilai Q(0) dan Q'(1), output akan berubah apabila input J dan K bernilai 1 0 atau 1 1. Nilai input selalu mengikuti nilai Clock.

2. Analisa apa yang terjadi saat B5 dan B6 dihubungkan ke Clock. Gambarkan timing diagramnya.

Jawab:

Pada saata input B5(D) dan B6(CLK) dihubungkan ke clock berakibatkan output Q selalu bernilai 1 dan output Q' selalu bernilai 0 karena kebalikan dari output Q. Karena output D Flip Flop terjadi pada saat rise time yang dimana rise time itu sendiri adalah kondisi dari low ke high, sehingga outputnya tidak berubah.

a. HTML

b. Video

Comments

Post a Comment