Laporan Akhir Percobaan 1 Kondisi 5

Laporan Akhir Percobaan 1 Kondisi 5

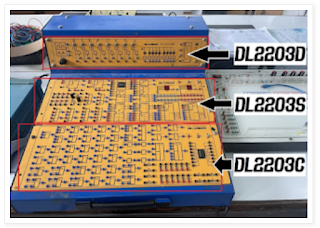

Pada percobaan kali ini membuat rangkaian yang sesuai dengan gambar percobaan 1, yaitu 4 buah J K Flip Flop dengan 7 saklar. Dimana SW 1 terhubung dengan SET pada J K Flip Flop terakhir, SW 2 terhubung dengan SET pada J K Flip Flop ke 3, SW 3 terhubung dengan SET pada J K Flip Flop kedua, SW 4 terhubung dengan SET pada J K Flip Flop pertama. SW 5 pada gerbang AND, SW 6 pada input J dan K pada Flip Flop yang pertama dan SW 7 terhubung dengan RESET pada seluruh Flip Flop.

Pada percobaan kali ini memvariasikan nilai B0-B6, dari input-input ini kami dapatkan hasil yaitu untuk B3-B6=0, B0 dan B2=1 serta B1=X maka kami dapatkan rangkaiannya Serial In Serial Out (SISO). B3-B6=0, B0=1 dan B2=Rise Time serta B1=X maka kami dapatkan rangkaiannya Serial In Pararel Out (SIPO). B3-B6=X, B0 dan B2=1 serta B1=0 maka kami dapatkan rangkaiannya Pararel In Serial Out (PISO). B3-B6=X, B0=1 dan B2=0 serta B1=0 maka kami dapatkan rangkaiannya Pararel In Pararel Out (PIPO).

5. Video Rangkaian[Kembali]

1. Analisa output yang dihasilkan tiap tiap kondisi

Jawab:

a. Kondisi 1 : SISO (Serial In Serial Out), karena datanya masuk secara berurutan/ satu-satu, dan untuk keluarannya terletak pada output ke-4 flip flop yang dimana untuk keluarannya itu juga satu-satu.

b. Kondisi 2 : SIPO (Serial In Parelel Out), karena datanya masuk secara berurutan / masuk satu-satu, dan untuk outputnya keluar secara serempak.

c. Kondisi 3 : PISO (Parelel In Serial Out), karena data tersimpan atau dimasukkan pada jalur masing-masing flip flop yang diinputkan dari switch B3-B6 dan tersimpan atau keluar melalui satu jalur yang sama.

d. Kondisi 4 : PIPO ( Paralel In Paralel Out), karena mempunyai jalur masukan dan keluaran sesuai dengan jumlah flip flop yang menyusunnya dan pada PIPO data yang masuk dan data keluarnya serempak.

2. Jika gerbang AND pada rangkaian dihapus, sumber clock dihubungkan langsung ke flip flop, bandingkan output yang didapatkan.

Jawab:

Outputnya yang didapatkan berbeda jika menghilangkan gerbang AND, karena jika gerbang AND di hapus maka shift register SIPO dan PIPO tidak ada.

a. HTML

b. Video

Comments

Post a Comment